IO模拟I2S总线方法

举报

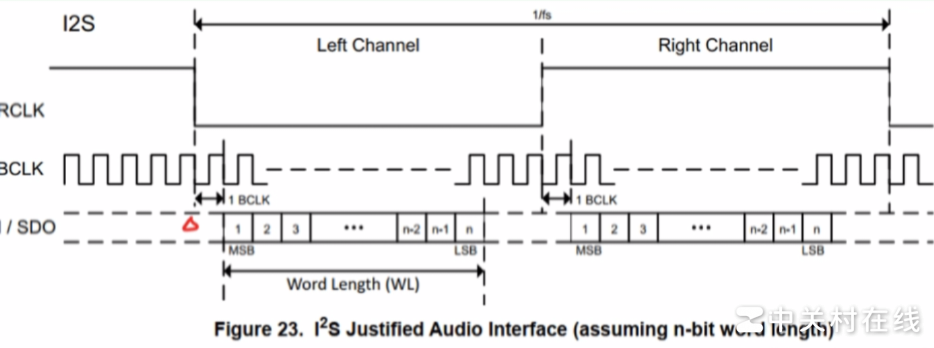

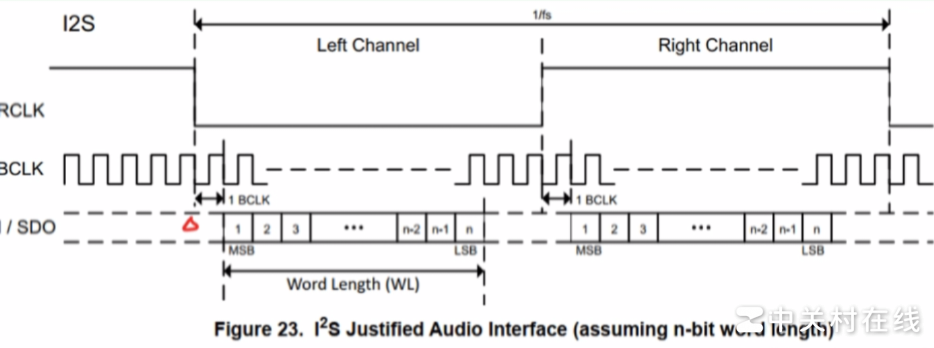

在i2s总线中,

声道切换由帧时钟LRCLK控制,其频率为44.1kHz,对应电平宽度约为11.34微秒。

位时钟BCLK频率为1.4 MHz,对应周期约0.71微秒,其高电平或低电平持续时间仅为0.35微秒。

最难之处在于高位数据的高字节,需滞后LRCLK一个BCLK周期。

——————————————————

模拟I²C通信时,通过延时即可实现。

模拟音频I2S传输通常需依赖定时器实现。

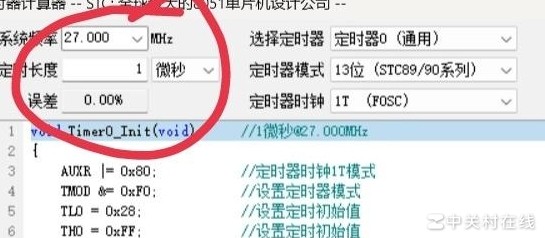

然而,STC-ISP支持的最小定时单位为1微秒。如何进一步提升计时精度?常见方法是插入NOP指令进行微调。

另一个关键问题是确保三条数据线之间的时序同步协调。

例如,在一个BCLK周期内,需先将BCLK信号置高,再按指定时长拉低。

还需同步传输一位数据,需判断其为0或1,并据此拉高或拉低总线,该判断与操作过程本身亦消耗时间。

——————————————————

我是初学者,若有表述不当之处,敬请谅解。借此问题,也想了解一些实用思路,例如:如何在相同时间内高效统筹并行的两项任务?